1. Gate S-R 래치

특정 타이밍에 S-R 래치를 동작시키기 위해서 NAND 게이트 외에 OR 게이트를 2개 추가하고 gate 입력 신호를 추가한다. S-R 래치의 입력을 on/off로 통제하기 위해서 사용한다.

동작 방식을 생각해보자. gate에 1을 주어 gate-bar가 0의 값을 가질 때는, set-bar, reset-bar가 어떤 값이냐에 따라서 출력인 Q, Q-bar가 유지될지 말지가 결정된다. 그러나 gate에 0을 주어 gate-bar가 1이 된다면, set, reset값과 상관없이 OR 게이트를 거치게 되어있으므로 NAND로 들어가는 입력들이 반드시 1이 들어가서 Q, Q-bar의 값이 유지된다. 다시말해 gate의 입력값이 0일때는 반드시 출력값이 유지되도록 해주는 것이다.

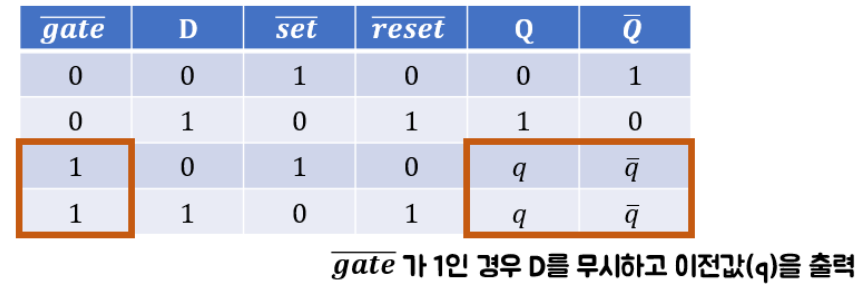

2. Gate D 래치

gate D latch는 Gate SR 래치에서 입력값을 1개로 두는 회로이다. 아래 그림처럼 입력값 D가 set-bar, reset-bar로 분기되도록 설계한다. 그리고 NOT 게이트를 이용하여 set, reset을 반전시켜 입력하므로 set, reset이 서로 반대되는 보수의 특성을 갖는다.

set, reset이 보수 관계가 되도록 설계했기 때문에, 입력이 둘다 1, 1인 입력금지의 경우가 발생하지 않는다는 장점이 있다.

3. 플립플롭

플립플롭의 원리

플립플롭은 1비트를 기억하기 위한 소자임과 동시에, 스위치 on/off, toggle 의 기능을 지원하는 논리회로이다. 앞서 배운 래치는 입력에 따라 출력이 항상 반영되는 반면, 플립플롭은 클럭의 순간적인 상태변화(엣지) 시점에 입력이 출력에 반영되는 것이다. 엣지란 논리 수준이 0 -> 1, 1 -> 0 등으로 전이되는 것을 의미한다.

종류는 다음과 같다.

- RS 플립플롭

- JK 플립플롭

- D 플립플롭

- T 플립플롭

- 마스터-슬레이브 플립플롭

RS 플립플롭의 원리를 이해하면, 나머지는 쉽게 이해할 수 있다. 입력으로 S(Set), R(Reset), CP(Clock Pulse)가 있고 출력으로 Q, Q-bar가 있다. Q와 Q-bar는 보수 관계로 항상 반대값을 가져야만 한다. 기존 출력 상태와 입력에 따른 출력 변화 상태를 나타내기 위해 Q_n, Q_n+1을 표시한다.

어려울게 없다. 만약 위 상태에서 Q가 0일 때, S, R에 각각 0을 넣는다고 가정해보자. 그럼 CP로 1값을 줬을 때 아래 그림과 같이 각 부분에서 출력값이 결정되는 것을 볼 수 있다. 그리고 Q, Q-bar 값은 그대로 유지되는 결과가 나온다.

반대로 초기 Q값이 1일 때도 입력값이 0, 0 이라면 출력값이 1로 유지되는 것을 확인할 수 있다. Q-bar도 0으로 유지된다. 즉 RS 플립플롭에서 입력값으로 0, 0을 넣으면 원래의 출력값이 유지되는 것이다.

만약 Set, Reset에 해당하는 2개의 버튼이 있어서 입력값을 줄 수 있는 상황이라면, 버튼을 아무것도 안 누르는 경우 플립플롭 회로에서는 출력값의 변화가 없이 유지가 되는 것이다.

이런 식으로 하나씩 해보면, RS 플립플롭의 입력에 따른 출력값, 특성표를 얻을 수 있다.

입력값의 이름이 Set, Reset인 이유를 알 수 있다. R이 1이면 다음 상태를 0으로 Clear 해주고, S가 1이면 다음 상태를 1로 Set 해주는 것이다.

래치때와 마찬가지로, Set, Reset이 둘 다 1의 입력을 갖는 경우는 출력의 보수관계가 깨지므로 허용하지 않는다. 이렇게 입력의 경우의 수가 낭비되는 것을 보완하기 위해서 아래의 JK 플립플롭이 등장하게 되었다.

J-K 플립플롭

JK 플립플롭은 RS 플립플롭에서 입력이 둘 다 1일때를 사용하기 위해서 AND 게이트를 추가해주는 것이다.

Q 출력이 J의 AND 게이트로 되먹임되고, Q-bar의 출력이 K의 AND 게이트로 되먹임 되면 J, K 가 모두 1, 1인 경우에는 toggle 기능이 동작됨을 알 수 있다. toggle이란 키보드에서의 caps lock, 한/영 키와 같이 상태값을 바꿔주는 기능을 말한다. 여기서는 (Q, Q-bar)의 값을 뒤집어주는 경우를 뜻한다. 다시말해 (1, 0) -> (0, 1), (0, 1) -> (1, 0)으로 바꿔준다.

JK 플립플롭은 2개의 입력값의 경우의 수 4개를 모두 사용할 수 있도록 해준다.

D플립플롭, T플립플롭, 마스터-슬레이브 플립플롭

D 플립플롭은 플립플롭의 4가지 경우 중 입력이 (0, 1), (1, 0)에 해당하는 2가지만 사용하는 플립플롭이다. T 플립플롭은 (0, 0), (1, 1)의 2가지 경우만 사용한다. 각각 on/off만 사용하거나, 유지/toggle 기능만 사용하는 것이다.

마스터-슬레이브 플립플롭은 JK 플립플롭의 타이밍으로 인한 오류 때문에 사용한다. JK 플립플롭의 특성상 한번 회로를 거친 출력이 다시 입력값으로 들어가야하는데, 물리적/기계적 한계로 인해 되먹임된 입력이 출력으로 나오는 것이 아니라, 처음 나온 출력이 바로 최종 출력으로 전달되는 현상이 나타날 수 있다. 이런 현상을 Race 현상이라고 한다. 그래서 종종 오류가 발생하며 race 현상을 해결하기 위해서 2개의 JK 플립플롭을 붙여서 해결하는 구조를 마스터-슬레이브 플립플롭 구조라고 한다.

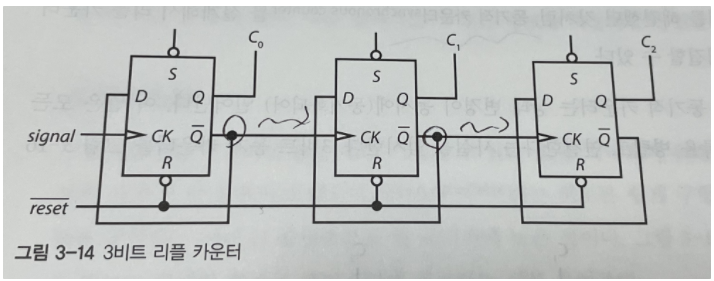

4. 카운터

카운터는 플립플롭은 응용한 수를 세는 순차 회로 모듈이다. 비트값을 저장할 수 있기 때문에 그것을 기반으로 수를 셀 수도 있는 것이다. 플립플롭을 기반으로 하기 때문에 플립플롭의 수와 연결 방식에 따라서 카운트 할 수 있는 최대값이 결정된다.

아래 그림들과 같이 플립플롭의 클럭펄스가 연결된 형태이다. 비동기식 카운터(리플 카운터)는 공통 클럭을 사용하지 않기 때문에 플립플롭 동작 시간이 불일치하여 타이밍 문제가 발생할 수 있다. 동기 카운터는 공통 클럭이 병렬로 연결되어 동작시간이 일치하는 카운터이다.

참조

0. [책] 한 권으로 읽는 컴퓨터 구조와 프로그래밍

1. My.log 블로그

2. 최희준 교수의 컴퓨터 일반 - 플립플롭

'Computer Science > Introduction' 카테고리의 다른 글

| 혼자 공부하는 컴퓨터구조 + 운영체제: 1. 컴퓨터 구조 개요, CPU의 동작 (0) | 2022.12.04 |

|---|---|

| 12. 중앙 처리 장치, 레지스터 (0) | 2022.05.15 |

| 10. 시간표현과 상태기억: 발진자, 클럭, 래치 (0) | 2022.05.01 |

| 9. [종합][스터디] 드 모르간의 법칙, 2의 보수, UTF-8, Base64 인코딩 이유 (0) | 2022.04.27 |

| 8. 가산기, 디코더/인코더, 멀티플렉서/디멀티플렉서 (0) | 2022.04.19 |