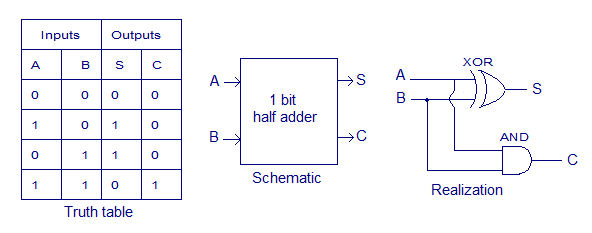

1. 반가산기(Half Adder)

반가산기는 두 비트가 더해졌을 때 올림 자리수(Carry, C)는 표시만 하고, 합계 자리수(Sum, S)만 계산할 수 있는 논리 회로이다.

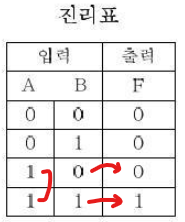

0과 0을 더하면 합계 S 도 0, 올림도 없으므로 0이다. 이런식으로 진리표(Truth Table)이 작성된다. 그런데 S의 결과와 C의 결과를 보면, S는 XOR 연산자, C는 AND 연산자임을 알 수 있다. 따라서 기계적으로는 XOR, AND 게이트가 합쳐진 논리회로로 표현되는 것이다.

진리표를 보고 논리식으로 쓰면 S = A'B + AB' = A ⊕ B 이다(⊕ = XOR 기호). C = A · B 이다.

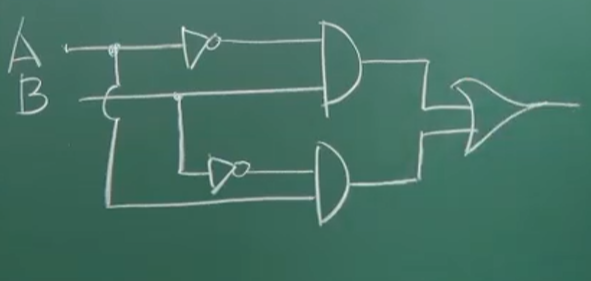

이전 시간에 배웠던 방법대로 A'B + AB' 논리식을 논리 회로로 표현해보면 아래 그림과 같이 표현된다.

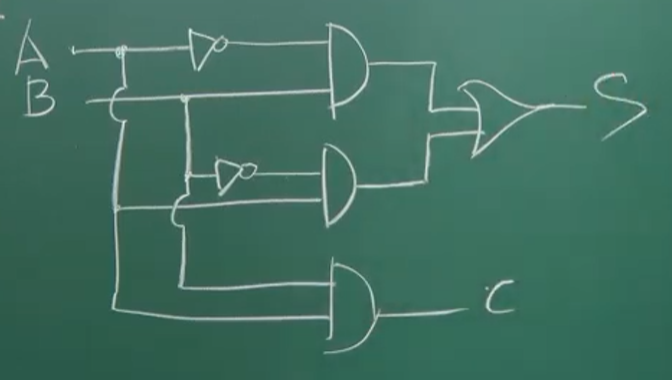

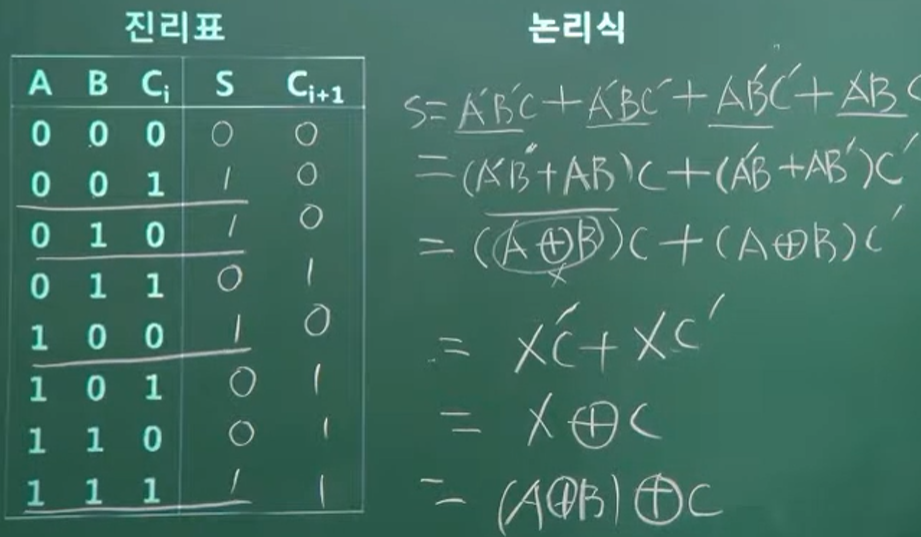

2. 전가산기(Full Adder)

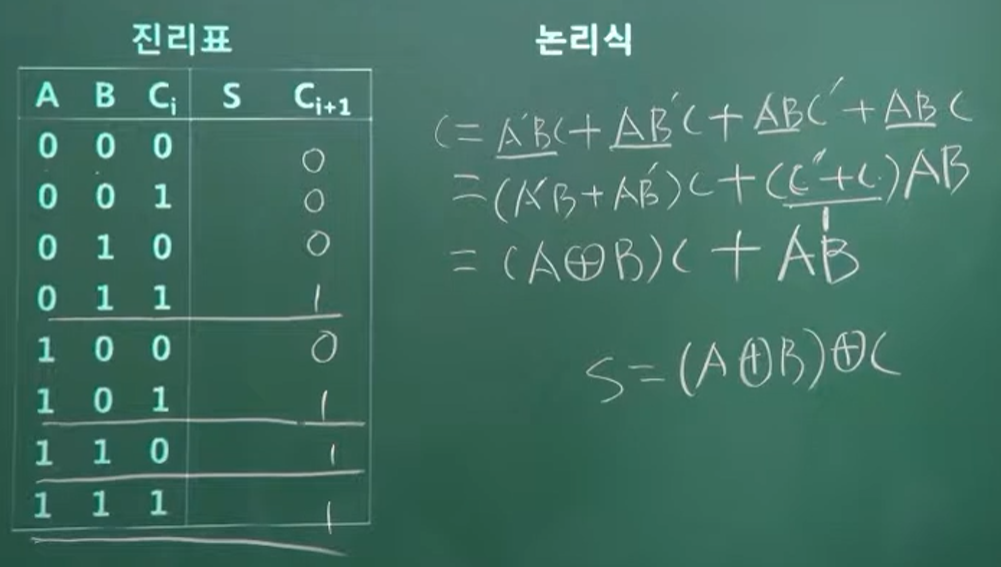

전가산기는 두 비트에 1개의 Carry 비트(C_i)를 더해서 합 S와 또 다른 Carry, C_i+1을 구하는 것이다.

Sum, 합계 S 구하기

반가산기를 구할때와 같다. 진리표를 구하고, S와 C_i+1에 대한 논리식을 간략화하여 표현하면 된다.

다만 여기서 A'B' + AB는 XNOR =

로 표현한다. 그리고 A'B + AB' = XOR = A ⊕ B 이다.

S = (A ⊕ B) ⊕ C 이다.

Carray, 올림 C 구하기

C = (A ⊕ B) C + AB 이다.

회로 그리기

전가산기는 2개의 반가산기와 1개의 OR 게이트로 구성된다.

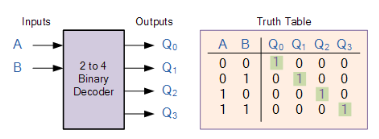

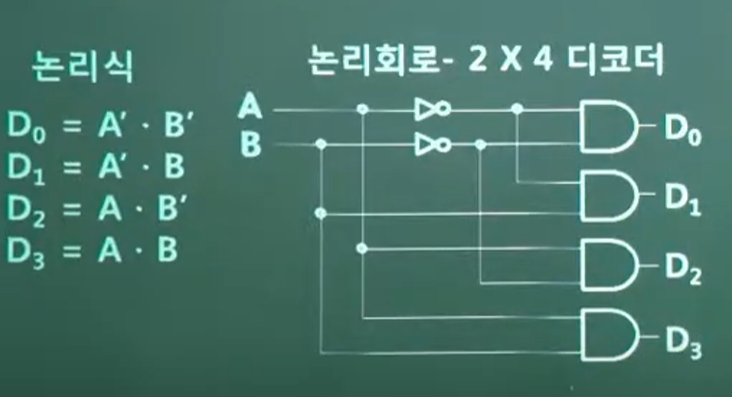

3. 디코더(Decoder)

디코더는 n개 비트의 입력 정보를 2^n개의 출력 정보로 변환하는 회로이다. 보통 디코더는 2 x 4(2^2), 3 x 8(2^3), 4 x 16(2^4) 디코더 등으로 부른다. 이것은 입력 수에 따른 출력이 일대일 대응함수인 경우를 표현하는 것이라고 보면 된다. 아래 그림처럼(참조 3).

2 x 4 디코더의 논리식 및 논리회로는 아래와 같다. 가산기에 비해서 쉽다!

디코더는 주로 주소값을 표시하는데 많이 사용한다.

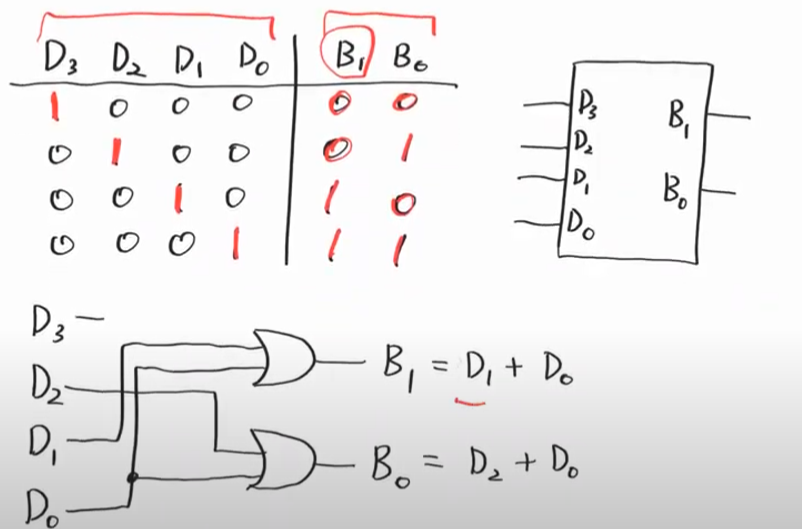

4. 인코더

디코더의 반대다. 2^n 개의 input에 대해서 n개의 output이 있다. 디코더랑 정확히 반대개념이라, 어렵지 않다.

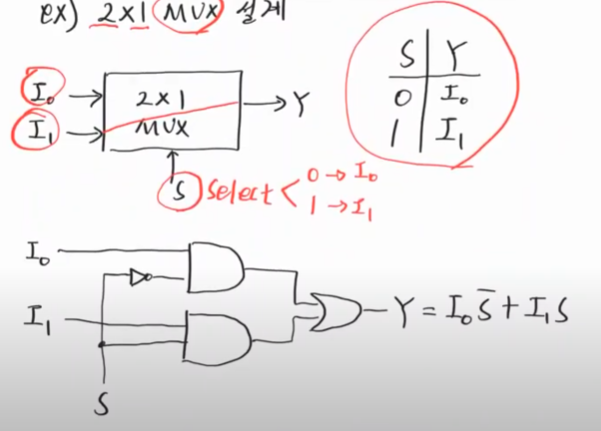

5. 멀티플렉서(Multiplexer, MUX)

멀티플렉서는 2^n개의 입력, n개의 선택선, 1개의 출력이 있는 형태이다. n개의 선택선에 의해서 하나의 입력이 선택되어 출력된다.

I_0, I_1의 값이 (0, 0), (0, 1), (1, 0), (1, 1)이 입력되었을 때, S가 1이냐 0이냐에 따라 출력이 달라진다. I_0, I_1은 S와 AND로 이어져 있다. 아래 AND 게이트의 진리표를 바탕으로, A에 I_0나 I_1 값을, B에 S 값을 매칭한다고 생각해보자. 추가된 주석을 보면, AND 게이트의 특성 하나를 생각해볼 수 있을 것이다.

AND 게이트는 하나의 입력이 1일 때, 출력은 나머지 값으로 결정된다.

즉 위 멀티플렉서에서, S가 0이나 1일 때 I_0, I_1이 있는 각 AND 게이트쪽으로 NOT 게이트를 거쳐 분기되므로, S의 입력값에 따라서 I_0 또는 I_1이 출력되는 것이다. 결국 논리식은 그림에 있는 대로 표현할 수 있다.

멀티플렉서는 여러 아날로그/디지털 입력을 하나의 출력으로 뽑아낼 때 유용하게 사용한다고 한다.

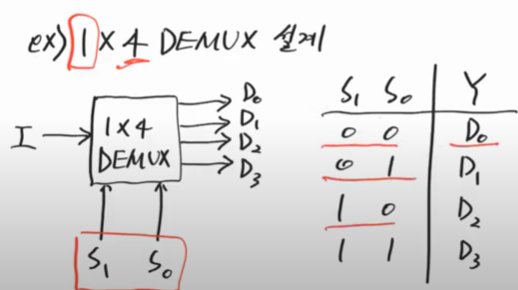

6. 디멀티플렉서(demultiplexer, DMUX)

디멀티플렉서는 인코더/디코더의 관계와 같이, 멀티플렉서의 반대 개념이다.

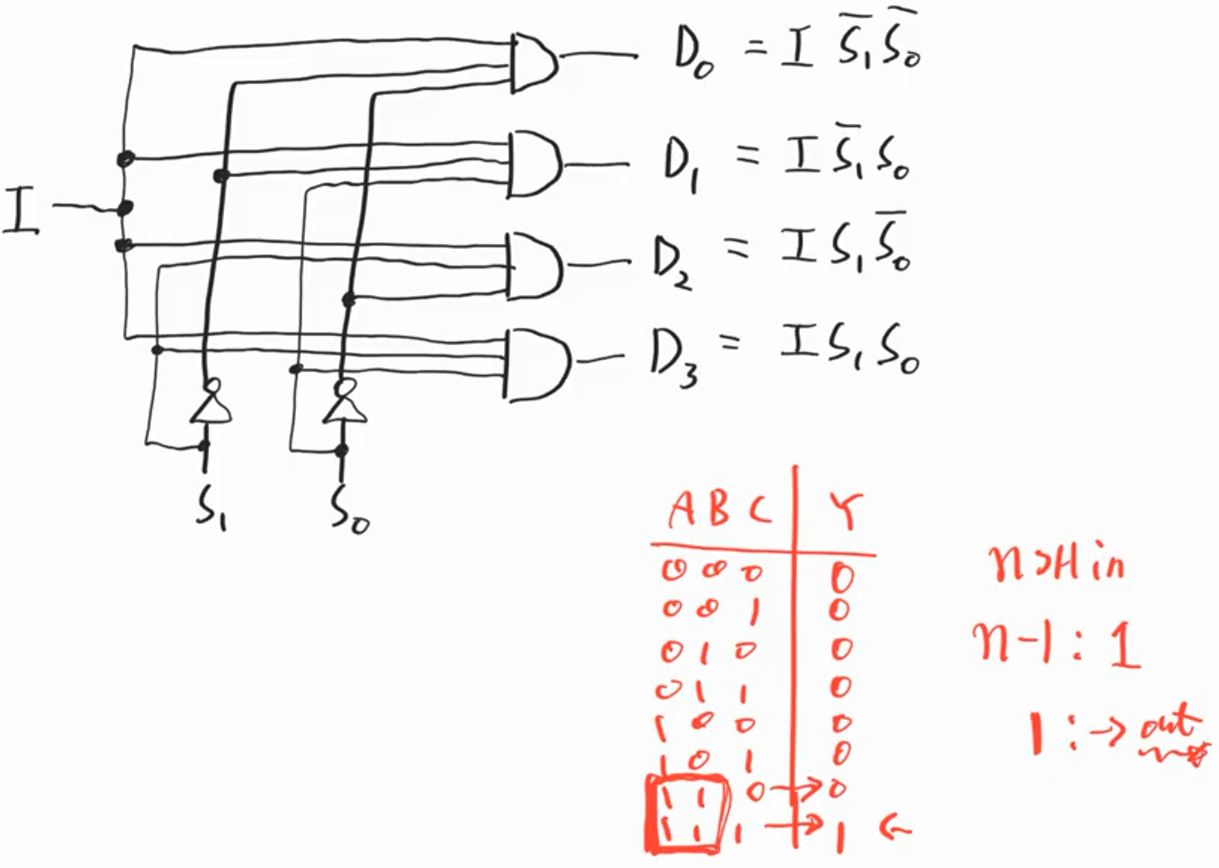

이번엔 1 x 4 Demux의 설계를 예시로 든다. 참조 4의 강의에서 설명에서, 위 멀티플렉서에서 살펴본 AND 게이트의 속성을 3개의 입력에 대해서 설명한다.

입력이 여러 개 일때, AND 게이트는 n-1개의 입력이 1인 상태라면 출력은 나머지 1개의 값을 따른다는 것이다. 이 로직대로 회로도가 위 그림처럼 표현될 수 있다.

상기 살펴본 논리 회로 소자들은 회로도로 그려놓은 것과 같이 그대로 회로 설계에 이용하지는 않는다. 실제로는 PMOS, NMOS 등을 활용하고, 좀 더 간단한 논리게이트 등을 사용하는 등 더 발전된 기술들이 적용된다. 그러나 이 글의 목적은 논리 회로 및 소자가 어떤 것들이 있고 어떻게 구성되는지만 이해하는 정도이므로 여기서 마친다.

참조

0. [책] 한 권으로 읽는 컴퓨터 구조와 프로그래밍

1. 길벗 시나공 IT

https://www.youtube.com/watch?v=W1xc4tDICMc

2. 나무숲 블로그

https://woodforest.tistory.com/122

3. Electronics Tutorials

https://www.electronics-tutorials.ws/combination/comb_5.html

4. 유튜브 - 바쁜직장인 : 논리회로(디지털공학)10강 인코더,디코더,멀티플렉서,디멀티플렉서(Encoder, Decoder, MUX, DeMUX)

https://www.youtube.com/watch?v=YZRLdFowL9s

'Computer Science > Introduction' 카테고리의 다른 글

| 10. 시간표현과 상태기억: 발진자, 클럭, 래치 (0) | 2022.05.01 |

|---|---|

| 9. [종합][스터디] 드 모르간의 법칙, 2의 보수, UTF-8, Base64 인코딩 이유 (0) | 2022.04.27 |

| 7. (보충) 논리식의 간소화 (0) | 2022.04.18 |

| 6. (보충) 출력유형 : Open Collector, Push Pull, Totem Pole (0) | 2022.04.17 |

| 5. 이력현상, 차동신호, 전파지연 (1) | 2022.04.10 |