1. 이력현상(Hysteresis)

이력현상은 어떤 시스템의 출력이 단순히 입력에 의존하는 것이 아니라, 입력이 시간에 따라 변화해온 이력에 따라 출력이 달라진다는 것을 의미한다. 말이 어렵다. 아래 StackOverflow의 참조를 보면, thermostat(열전대)의 예시를 든다.

source : 유튜브-열전대 작동 방식

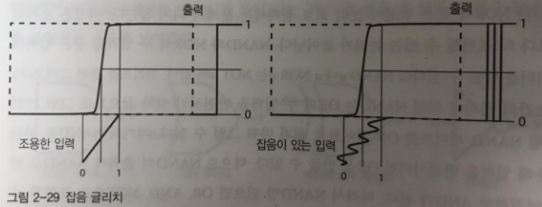

참고로만 하고, 만약 가열하여 온도가 70℃가 되면 스위치가 ON되고, 냉각하여도 70℃가 되면 스위치가 OFF 되는 시스템이 있다고 가정하자. 그럼 아래 서적에서 전기신호가 잡음(Glitch)가 있는 상황이라면 스위치가 ON, OFF를 반복하며 진동하여 불안정한 시스템이 될 것이다.

이때 이력현상을 이용한다. 즉 가열하여 온도가 올라가는 구간에서는 시스템이 ON되는 문턱값을 71℃로 설정하고, 냉각하여 온도가 내려가는 구간에서는 시스템이 OFF되는 문턱값을 69℃로 설정하자. 1℃의 여유분이 있기 때문에 시스템이 좀 더 안정적으로 동작하리라 예상될 것이다. 컴퓨터 공학에서도 잡음에 대한 내성을 위해 0과 1사이의 0.5의 값을 단순하게 문턱값(threshold)로 잡는 것이 아니라, 0이나 1에 매우 가까운 값으로 문턱값을 잡는다. 이력 현상을 이용하는 것이다.

슈미트 트리거(Schmitt trigger) 게이트 : 이력현상을 이용한 트랜지스터이다. 일반 게이트보다 복잡하고 비싸기 때문에 정말 꼭 필요한 경우만 사용한다.

2. 차동 신호(Differential signaling)

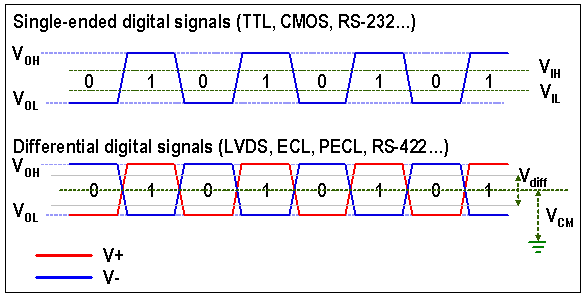

차동신호는 이력현상만으로 해결하기 힘든 아주 큰 잡음이 들어왔을 때 이를 해결하기 위한 방법으로 사용하는 것이다. 위 그림과 같이 위상이 정확히 반대인 V+, V- 신호를 함께 입력값으로 전송하는 형태이다. 이렇게 하면 잡음에 대한 내성이 강해진다. 왜 그럴까?

비교를 위해 Single-ended digital signals 그래프를 보자. 0, 1, 0, 1, .. 신호가 반복된다. 그런데 여기에 만약 잡음이 생겨서 0.1, 0.7, 0.4, 0.6, ...과 같이 불안정한 입력신호가 전송된다고 해보자. 그럼 신호를 받아들이는 곳에서 이 신호가 원래 0, 1, 0, 1, ... 을 보내온 것인지 알기가 매우 어렵다. 이제 Differential digital signals를 보자. (1,0), (0,1), ... 으로 입력 신호가 오다가 잡음이 발생하는 경우를 상상해보자. 두 신호가 겪는 물리적 상황은 거의 동일하므로 잡음에 대해 받는 영향이 같은 수치로 변하게 될 것이다. 즉 (0.8, -0.2), (0.3, 1.3), ...과 같이 두 신호의 차이값은 거의 일정한 Vdiff값으로 유지될 것이다. 이를 통해 수신부에서는 입력부의 신호가 원래 어땠는지 해석할 방법을 찾게 된다.

source : https://www.autodesk.com/products/eagle/blog/what-is-differential-signaling/

3. 전파지연

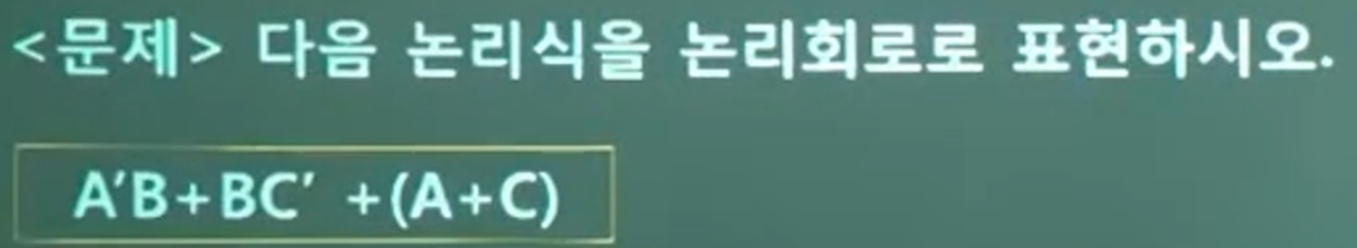

전파지연을 이해하기 위해서는 논리 게이트 작동방식과 논리 회로의 타임 차트에 대해서 이해하고 있어야한다.

논리 게이트 작동 방식

- A AND B 는 AB와 같이 붙여서 쓴다.

- A OR B 는 A + B처럼 덧셈 기호로 쓴다.

아래 링크의 문제를 보자. 입력 A, B에 대해서 출력 Y가 발생한다. 필기로 처리된 부분을 입력부분부터 차분히 살펴보면 쉽게 이해할 수 있다.

위 내용이 이해가 됬다면, 다음 문제도 스스로 풀어보면 된다. 연습장에 그려보면 쉽게 이해할 수 있다. 혹시나 어렵다면 참조 링크의 영상을 보면 된다.

source : https://www.youtube.com/watch?v=Hal8NrGao9I

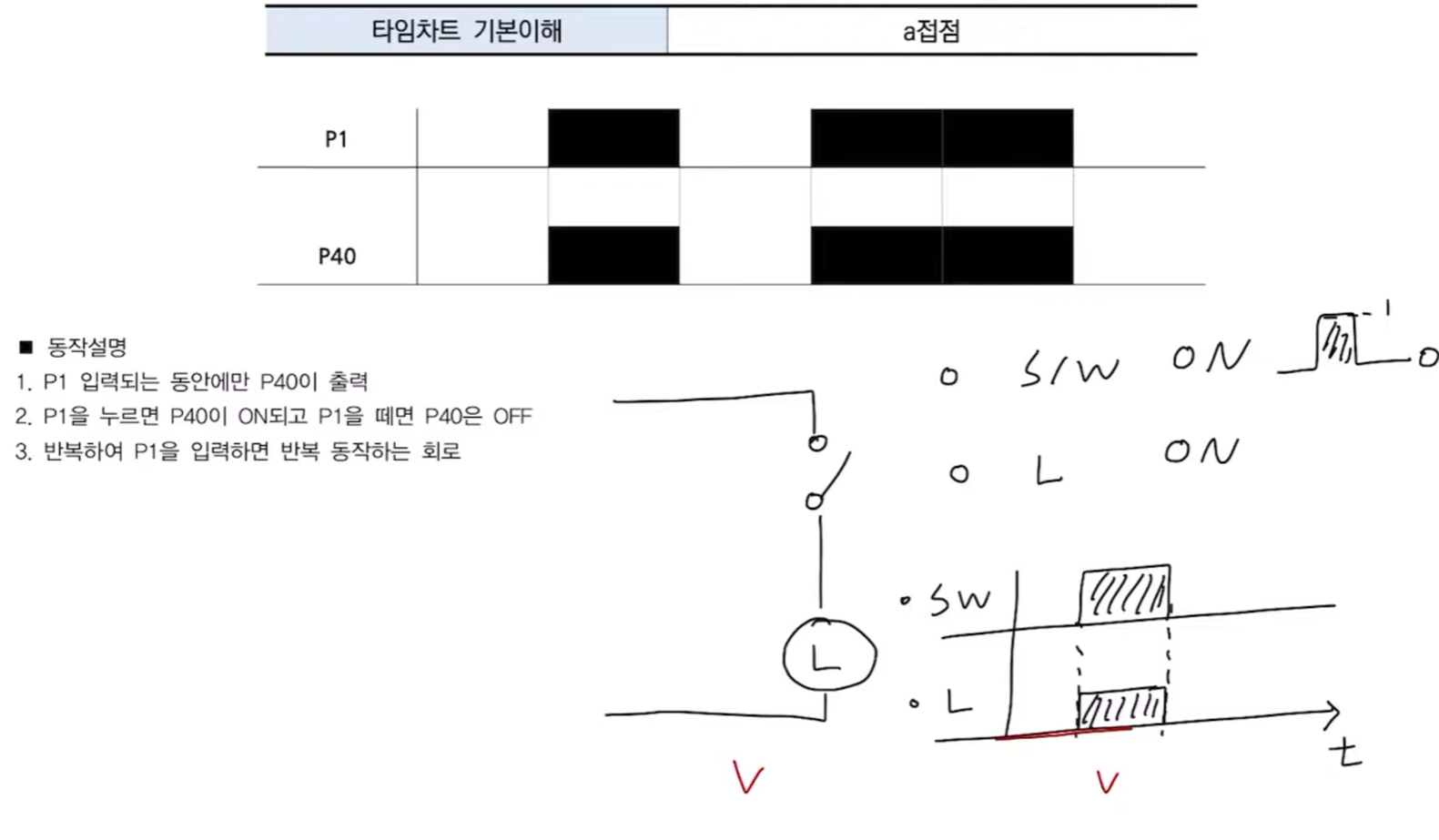

논리 회로의 타임 차트

타임 차트는 더 쉽다. 똑같이 2가지만 기억하면 된다.

1. 원인-결과로 이루어진다.

2. 반복하며 시간에 따른 동작 상태를 그린다.

P1은 입력이고, P40은 출력이다. 아래 시퀀스도(회로도) 에서, P1은 스위치이고 P40은 L로 표시된 램프이다. 스위치가 켜지면, Lamp도 켜진다. 반대로 스위치가 꺼지면 Lamp도 꺼진다. 쉽다.

source : https://www.youtube.com/watch?v=4eG__HzsQ8k

전파 지연

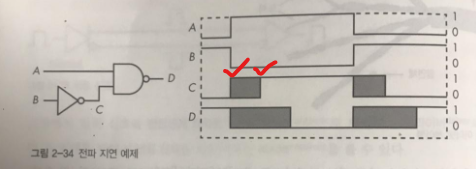

이제 책에 나온 전파 지연 예제 그림을 해석해본다.

입력은 A, B, 출력은 C, D 이다. 왼쪽에서부터 입력값이 변할 때마다 일어나는 상황에 대해 시간에 따른 출력 변화를 그려낸 것이다.

1. A = 0 , B = 1

- Not B = C 이므로 C = 0이다.

- Not (A AND C) = D 이므로 D = 1 이다. (Not AND = NAND = 입력이 둘 다 0일때만 1)

2. A = 1, B = 0

그림에서 첫번째 빨간 체크 표시가 있는 부분을 보자.

- Not (A AND C) = D 이므로 D = 0이다.

-> 첫 번째 빨간 체크 표시에서, C는 즉시 1이되고 D는 즉시 0이 된다. 그러나 전파 지연때문에 실제로는 두번째 빨간 체크 표시와 같이 동작한다는 것이다. 또한 D는 C의 출력을 받아서 동작하기 때문에, D의 지연은 C의 지연 이후에 더 지연 시간이 추가된 것처럼 그려졌다.

이렇게 0(Low) 에서 1(High)로 갈때의 지연을 Propagation time from Low to High 라고 해서 보통 전자 부품에서 t_PLH로 표시하고, 반대는 t_PHL로 표시한다.

현대 부품에서 대부분의 이런 전파 지연은 피코초(ps, 10의 -12승) 정도이다.

참조

1. [책] 한 권으로 읽는 컴퓨터 구조와 프로그래밍

'Computer Science > Introduction' 카테고리의 다른 글

| 7. (보충) 논리식의 간소화 (0) | 2022.04.18 |

|---|---|

| 6. (보충) 출력유형 : Open Collector, Push Pull, Totem Pole (0) | 2022.04.17 |

| 4. 비트처리 하드웨어 : 릴레이, 진공관, 트랜지스터, 논리게이트 (0) | 2022.04.10 |

| 3. 디지털 게인과 증폭 회로: gain, distortion, threshold, cutoff, saturation (0) | 2022.04.10 |

| 2. 컴퓨터 내부의 언어 체계 - 비트와 실수, 텍스트 표현 (0) | 2022.02.02 |